# Chapter 37 MIPI Controller

# **37.1 Overview**

The Display Serial Interface (DSI) is part of a group of communication protocols defined by the MIPI Alliance. The MIPI Controller is a digital core that implements all protocol functions defined in the MIPI DSI Specification. The MIPI Controller provides an interface between the system and the MIPI D-PHY, allowing the communication with a DSI-compliant display. The MIPI Controller supports one to four lanes for data transmission with MIPI D-PHY.

The MIPI Controller supports the following features:

- Compliant with MIPI Alliance standards

- Support the DPI interface color coding mappings into 24-bit Interface

- 16 bits per pixel, configurations 1,2,and 3

- 18 bits per pixel, configurations 1 and 2

- 24 bits per pixel

- Programmable polarity of all DPI interface signals

- Extended resolutions beyond the DPI standard maximum resolution of 800x480 pixels:

- Up to 2047 vertical active lines

- Up to 63 vertical back porch lines

- Up to 63 vertical front porch lines

- Maximum resolution is limited by available DSI Physical link bandwidth which depends on the number of lanes and maximum speed per lane

- All commands defined in MIPI Alliance Specification for Display Command Set (DCS)

- Interface with MIPI D-PHY following PHY Protocol Interface (PPI), as defined in MIPI Alliance Specification for D-PHY

- Up to four D-PHY Data Lanes

- Bidirectional communication and escape mode support through data lane 0

- Transmission of all generic commands

- ECC and Checksum capabilities

- End of Transmission Packet(EOTp)

- Ultra Low-Power mode

- Fault recovery schemes

# 37.2 Block Diagram

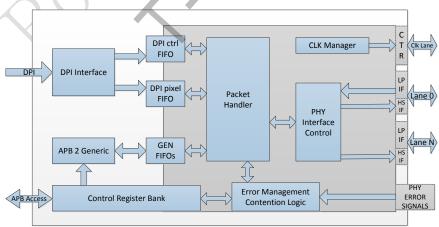

The following diagram shows the MIPI Controller architecture.

Fig. 37-1 MIPI Controller architecture

The DPI interface captures the data and control signals and conveys them to a FIFO for video

control signals and another one for pixel data. This data is then used to build Video packets, hen in Video mode.

The Register Bank is accessible through a standard AMBA-APB slave interface, providing access to the MIPI Controller registers for configuration and control. There is also a fully programmable interrupt generator to inform the system about certain events.

The PHY Interface Control is responsible for managing the D-PHY PPI interface. It acknowledges the current operation and enables low-power transmission/reception or a high-speed transmission. It also performs data splitting between available D-PHY lanes for high-speed transmission.

The Packet Handler schedules the activities inside the link. It performs several functions based on the interfaces that are currently DPI and the video transmission mode that is used (burst mode or non-burst mode with sync pulse or sync events). It builds long or short packet generating correspondent ECC and CRC codes. This block also performs the following functions: Packet reception, Validation of packet header by checking the ECC, Header correction and notification for single-bit errors, Termination of reception, Multiple header error notification.

The APB-to-Generic block bridges the APB operations into FIFOs holding the Generic commands. The block interfaces with the following FIFOS: Command FIFO, Write payload FIFO, Read payload FIFO.

The Error Management notifies and monitors the error conditions on the DSI link. It controls the timers used to determine if a timeout condition occurred, performing an internal soft reset and triggering an interruption notification.

# **37.3 Function Description**

# **37.3.1 DPI interface function**

TheDPI interface follows the MIPI DPI specification with pixel data bus width up to 24 bits. It is used to transmit the information in Video mode in which the transfers from the host processor to the peripheral take the form of a real-time pixel stream. This interface allows sending ShutDown (SD) and ColorMode (CM) commands, which are triggered directly by writing to the register of CFG\_MISC\_CON[2:1]. To transfer additional commands(for example, to initialize the display), use another interface such as APB Slave Generic Interface to complement the DPI interface.

The DPI interface captures the data and control signals and conveys them to the FIFO interfaces that transmit them to the DSI link. Two different streams of data are presented at the interface; video control signals and pixel data. Depending on the interface color coding, the pixel data is disposed differently throughout the dpipixdata bus. The following table shows the Interface pixel color coding.

Table 37-1 Color table

| Signal Line  | 16-bit   |          |          |          | 18-bit   | 24-bit |

|--------------|----------|----------|----------|----------|----------|--------|

|              | Config1  | Config2  | Config3  | Config1  | Config2  |        |

| dpipixdata23 | Not used | R7     |

| dpipixdata22 | Not used | R6     |

| dpipixdata21 | Not used | Not used | R4       | Not used | R5       | R5     |

| dpipixdata20 | Not used | R4       | R3       | Not used | R4       | R4     |

| dpipixdata19 | Not used | R3       | R2       | Not used | R3       | R3     |

| dpipixdata18 | Not used | R2       | R1       | Not used | R2       | R2     |

| dpipixdata17 | Not used | R1       | RO       | R5       | R1       | R1     |

| dpipixdata16 | Not used | RO       | Not used | R4       | RO       | RO     |

| dpipixdata15 | R4       | Not used | Not used | R3       | Not used | G7     |

| dpipixdata14 | R3       | Not used | Not used | R2       | Not used | G6     |

| dpipixdata13 | R2       | G5       | G5       | R1       | G5       | G5     |

| dpipixdata12 | R1       | G4       | G4       | R0       | G4       | G4     |

| dpipixdata11 | RO       | G3       | G3       | G5       | G3       | G3     |

| dpipixdata10 | G5       | G2       | G2       | G4       | G2       | G2     |

| dpipixdata9  | G4       | G1       | G1       | G3       | G1       | G1     |

| dpipixdata8  | G3       | G0       | G0       | G2       | G0       | G0     |

| dpipixdata7  | G2       | Not used | Not used | G1       | Not used | B7     |

| dpipixdata6  | G1       | Not used | Not used | G0       | Not used | B6     |

| dpipixdata5  | G0       | Not used | B5       | B5       | B5       | B5     |

| dpipixdata4  | B4       | B4       | B4       | B4       | B4       | B4     |

| dpipixdata3  | B3       | B3       | B3       | B3       | B3       | B3     |

| dpipixdata2  | B2       | B2       | B2       | B2       | B2       | B2     |

| dpipixdata1  | B1       | B1       | B1       | B1       | B1       | B1     |

| dpipixdata0  | BO       | B0       | Not used | BO       | BO       | BO     |

The DPI interface can be configured to increase flexibility and promote correct usage of this interface for several systems. These configuration options are as follows:Polarity control: All the control signals are programmable to change the polarity depending on system requirements.

After the MIPI Controller reset, DPI waits for the first VSYNC active transition to start signal sampling, including pixel data, and preventing image transmission in the middle of a frame.

If interface pixel color coding is 18 bits and the 18-bit loosely packed stream is disabled, the number of lines programmed in the pixels per lines configuration is a multiple of four. This means that in this mode, the two LSBs in the configuration are always inferred as zero. The specification states that in this mode, the pixel line size should be a multiple of four.

# 37.3.2 APB Slave Generic Interface

The APB Slave interface allows the transmission of generic information in Command mode, and follows the proprietary register interface. Commands sent through this interface are not constrained to comply with the DCS specification, and can include generic commands described in the DSI specification as manufacturer-specific.

The MIPI Controller supports the transmission or write and read command mode packets as described in the DSI specification. These packets are built using the APB register access. The GEN\_PLD\_DATA register has two distinct functions based on the operation. Writing to this register sends the data as payload when sending a Command mode packet. Reading this register returns the payload of a read back operation. The GEN\_HDR register contains the Command mode packet header type and header data. Writing to this register triggers the transmission of the packet implying that for a long Command mode packet, the packet's payload needs to be written in advance in the GEN\_PLD\_DATA register.

The valid packets available to be transmitted through the Generic interface are as follows:

Generic Write Short Packet 0 Parameters Generic Write Short Packet 1 Parameters Generic Write Short Packet 2 Parameter Generic Write Short Packet 0 Parameter Generic Write Short Packet 1 Parameters Generic Write Short Packet 2 Parameter Maximum Read Packet Configuration Generic Long Write Packet DCS Write Short Packet 0 Parameter DCS Write Short Packet 1 Parameter DCS Write Short Packet 0 Parameter

A set of bits in the CMD\_PKT\_STATUS register report the status of the FIFOs associated with APB interface support.

Generic interface packets are always transported using one of the DSI transmission modes; Video mode or Command mode. If neither of these mode are selected, the packets are not transmitted through the link and the released FIFOs eventually get overflowed.

The transfer of packets through the APB bus is based on the following conditions:

The APB protocol defines that the write and read procedure takes two clock cycles each to be executed. This means that the maximum input data rate through the APB interfaces is always half the speed of the APB clock.

The data input bus has a maximum width of 32 bits. This allows for a relation to be defined between the input APB clock frequency and maximum bi rate achievable by the APB interface.

The DSI link bit rate when using solely APB is equal to (APB clock frequency) \*16 Mbps.

The bandwidth is dependent on the APB clock frequency; the available bandwidth increases with the clock frequency.

To drive the APB interface to achieve high bandwidth Command mode traffic transported by the DSI link, the MIPI Controller should operate in the Command mode only and the APB interface should be the only data source that is currently in use. Thus, the APB interface has the entire bandwidth of the DSI link and does not share it with any another input interface source.

The memory write commands require maximum throughout from the APB interface, because they contain the most amount of data conveyed by the DSI link. While writing the packet information, first write the payload of a given packet into the payload FIFO using the GEN\_PLD\_DATA register. When the payload data is for the command parameters, place the first byte to be transmitted in the least sgnificant byte position of the APB data bus.

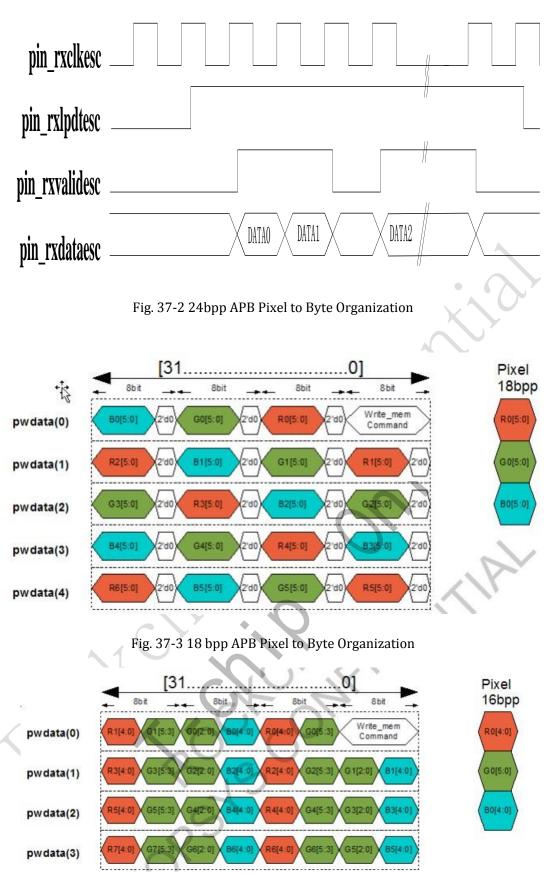

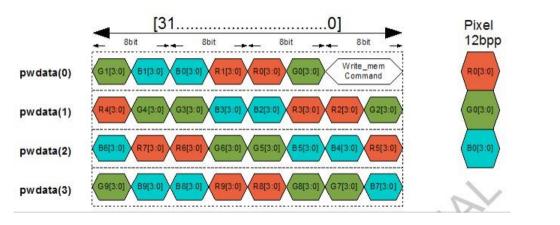

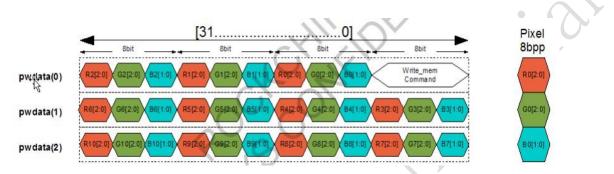

After writing the payload, write the packet header into the command FIFO. For more information and it should follow the pixel to byte conversion organization referred in the Annexure A of the DCS specification. The follow figures show how the pixel data should be orgavized in the APB data write bus. The memory write commands are conveyed in DCS long packets. DCS long packets are encapsulated in a DSI packet. The DSI included in the diagrams.In the follow figures, the Write Memory Command can be replaced by the DCS command Write Memory Start and Write Memory Continue.

Fig. 37-4 16 bpp APB Pixel to Byte Organization

Fig. 37-5 12 bpp APB Pixel to Byte Organization

Fig. 37-6 8bpp APB Pixel to Byte Organization

# **37.3.3 Transmission of Commands in Video Mode**

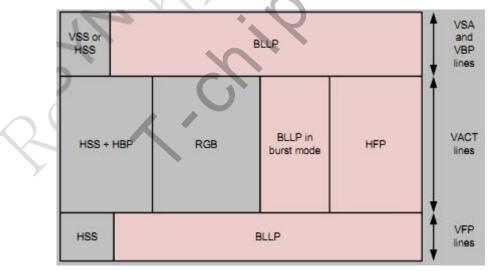

The MIPI Controller supports the transmission of commands, both in high-speed and low-power, while in Video mode. The DSI controller uses Blanking or Low-Power(BLLP) periods to transmit commands inserted through the APB Generic interface. Those periods correspond to the shaded areas of the following figure.

Fig. 37-7 Command Transmission Periods within the Image Area

Commands are transmitted in the blanking periods after the following packet/states:

- Bertical Sync Start (VSS) packets, if the Video Sync pulses are not enabled

- Horizontal Sync End (HSE) packets, in the VSA, VBP, and VFP regions

- Horizontal Sync Start (HSS) packets, if the Video Sync pulses are not enabled in the VSA,

VBP, and VFP regions

• Horizontal Active (HACT) state

Only one command is transmitted per line, even in the case of the last line of a frame but one command is possible for each line.

The MIPI Controller avoids sending commands in the last line because it is possible that the last line is shorter than the other ones. For instance, the line time (tL) could be half a cycle longer than the tL on the DPI interface, that is, each line in the frame taking half a cycle from time for the last line. This results in the last line being (1/2 cycle) \* (number of lines -1) shorter than tL.

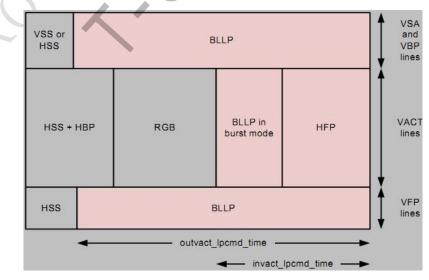

The dpicolorm and dpishutdn input signals are also able to trigger the sending of command packets. The commands are DSI data types Color Mode On, Color Mode Off, Shut Down Peripheral, and Turn on Peripheral. These commands are not sent in the VACT region. If the lpcmden bit of the VID\_MODE\_CFG register is 1, these commands are sent in LP mode. In LP mode, the ouvact\_lpcmd\_time field of the LP\_CMD\_TIM register is used to determine if these commands can be transmitted. It is assumed that outvact\_lpcmd\_time is greater than or equal to 4 bytes (number of bytes in a short packet), because the DWC\_mipi\_dsi\_host does not transmit these commands on the last line.

If the frame\_BTA\_ack field is set in the VID\_MODE\_CFG register, a BTA is generated by DWC\_mipi\_dsi\_host after the last line of a frame. This may coincide with a write command or a read command. In either case, the edpihalt signal is held asserted until an acknowledge has been received (control of the DSI bus is returned to the host).

If the lpcmden bit of the VID\_MODE\_CFG register is set to 1, the commands are sent in low-power in Video mode. In this case, it is necessary to calculate the time available, in bytes, to transmit a command in LP mode for Horizontal Front Porch (HFP), Vertical Sync Active (VSA), Vertical Back Porch (VBP), and Vertical Front Porch(VFP) regions.

The outvact\_lpcmd\_time field of the LP\_CMD\_TIM register indicates the time available (in bytes) to transmit a command in LP mode, based on the escape clock, on a line during the VSA, VBP, and the VFP

Outvact\_lpcmd\_time=(tL-(Time to transmit HSS and HSE frames +tHSA+Time to enter and leave LP mode+Time to send the D-PHY LPDT command)) / escape clock period / 8 / 2

Where,

tL=Line time

tHSA=Time to send a short packet (for sync events) or time of the HAS pulse (for sync pulses)

In the above equation, division by eight is done to convert the time available to bytes and division by two is done because one bit is transmitted once in every two escape clock cycles.

The outvact\_lpcmd\_time filed can be compared directly with the size of the command to be transmitted to determine if there is enough time to transmit the command. The maximum size of a command that can be transmitted in LP mode is limited to 255 bytes by this field. This register must be programmed to a value greater than or equal to 4 bytes for the transmission of the DCTRL commands such as shutdown and colorm in LP mode.

Consider an example with 12.6  $\mu$ s per line and assume an escape clock frequency of 15 MHz. In this case, 189 escape clock cycles are available to enter and exit LP mode and transmit command. The following are assumed:

Sync pulses are not being transmitted

Two lane byte clock ticks are required to transmit a short packet

phy\_lp2hs\_time=16 phy\_lp2p\_time=20 In this example, a 11-byte command can be transmitted as follows:

outvact\_lpcmd\_time=(12.6µs-(2\*10 ns)-(16\*10 ns)-(20\*10 ns)-(8\*66 ns)) / 66 ns / 8 / 2 = 11 bytes

The invact\_lpcmd\_time field of the LP\_CMD\_TIM register indicates the time available (in bytes) to transmite a command in LP mode (based on the escape clock) in the Vertical Active (VACT) region. This time is calculated as follows:

Invact\_lpcmd\_time=((tHFP-Time to enter and leave low-power mode + Blanking period before the HFP when in Burst mode- Time to send the D-PHY LPDT command) / escape clock period) / 8

Where,

tHFP=line time-tHSA-tHBP-tHACT tHACT=vid\_pkt\_size\*bits\_per\_pixel\*lane\_byte\_clock\_period / num\_lanes

The invact\_lpcmd\_time field can be compared directly with the size of the command to be transmitted to determined if there is time to transmit the command.

Consider an example where the refresh rate is 60 Hz. The number of lines is 1320 (typical). The tL in this case is 12.6µs. With a lane byte clock of 100 MHz, 1260 clock ticks are available to transmit a single frame. If 800 ticks are used for pixel data then 460 ticks (4.6µs) are available for Horizontal Sync Start (HSS), HFP, and HBP. Assuming that 2.3µs is available for HFP and the escape clock is 15MHz, only 34 LP clock ticks are available to enter LP, transmit a command, and return from LP mode. Approximately 12 escape clock ticks are required to enter and leave LP mode. Therefore, only 1 byte could be transmitted in this period.

A short packet (for example, generic short write) requires a minimum of 4 bytes. Therefore, in this exampled, commands are not sent in the VACT region. If Burst mode is enabled, more time is available to transmit commands in the VACT region. The following are assumed:

The controller is not in Burst mode

phy\_lp2hs\_time=16 phy\_lp2hs\_time=16

In this examplem invact\_lpcmd\_time is calculated as follows:

Invact\_lpcmd\_time =  $(2.3\mu s - (16*10 ns) - (20*10 ns) - (8*66 ns)) / 66 ns / 8 = 2 bytes$

The outvact\_lpcmd\_time and invact\_lpcmd\_time fields allow a simple comparision to determine if a command can be transmitted in any of the BLLP periods.

Fig. 38-8 illustrates the meaning of invact\_lpcmd\_time and outvact\_lpcmd\_time, matching them with the shaded areas and the VACT region.

Fig. 37-8 Location in the Image Area

If the lpcmden bit of the VID\_MODE\_CFG register is 0, the commands are sent in high\_speed in Video Mode. In this case, the DWC\_mipi\_dsi\_host automatically determines the area where each command can be sent and no programming or calculation is requied.

On read command Transmission, the max\_rd\_time field of the PHY\_TMR\_CFG register configures the maximum amount of time required to perform a read command in lane byte clock cycles.

The maximum time required to perform a read command in Lane byte clock cycles (max\_rd\_time) =Time to transmit the read command in LP mode + Time to enter and leave LP mode + Time to return the read data packet from the peripheral device.

The time to return the read data packet from the pripheral depends on the number of bytes read and the escape clock frequency of the peripheal; not the escape clock of the host. The max\_rd\_time field is used in both HS and LP mode to determine if there is time to complete a read command in a BLLP period.

In high-speed mode (lpcmden=0), max\_rd\_time is calculated as follows:

max\_rd\_time = phy\_hs2lp\_time + Time to return the read data packet from the peripheral device + phy\_hs2hs\_time

In low-power mode (lpcmden = 1), max\_rd\_time is calculated as follows:

max\_rd\_time = phy\_hs2lp\_time +LPDT command time + Read command time in LP mode + Time to return the data read from the peripheral device + phy\_lp2hs\_time

Where,

LPDT command time = (8\*Host escape clock period) / Lane byte clock periodRead command time in LP mode = <math>(32\*host escape clock period) / lane byte clock period

It is recommended to keep the maximum number of bytes read from the peripheral to a minimum to have sufficient time available to issue the read commands on a line. Ensure that max\_rd\_time\* Lane byte clock period is less than outvact\_lpcmd\_time \*8\*Escape clock period of the host.

Otherwise, the read commands are serviced on the last line of a frame and the edpihalt signal may be asserted. If it is necessary to read a large number of parameters (>16), increase the max\_rd\_time while the read command is being executed. When the read has completed, decrease the max\_rd\_time to a lower value.

# **37.4 Register Description**

This section describes the control/status registers of the design.

| Name             | Offset  | Size | Reset<br>Value | Description                                  |

|------------------|---------|------|----------------|----------------------------------------------|

| MIPIC_VERSION    | 0x00000 | w    | 0x3133302a     | Version of the mipi controller               |

| MIPIC_PWR_UP     | 0x00004 | W    | 0x0000000      | Core power-up                                |

| MIPIC_CLKMGR_CFG | 0x00008 | w    | $n_{n}$        | Configuration of the internal clock dividers |

| MIPIC_DPI_VCID   | 0x0000c | W    | 0x00000000     | The DPI interface configuration.             |

# 37.4.1 Registers Summary

| Name                        | Offset  | Size | Reset<br>Value | Description                                            |

|-----------------------------|---------|------|----------------|--------------------------------------------------------|

| MIPIC_DPI_COLOR_<br>CODING  | 0x00010 | W    | 0x00000000     |                                                        |

| MIPIC_DPI_CFG_POL           | 0x00014 | W    | 0x0000000      |                                                        |

| MIPIC_LP_CMD_TIM            | 0x00018 | W    | 0×00000000     | Low-power Command<br>Timing Configuration<br>Register. |

| MIPIC_PCKHDL_CFG            | 0x0002c | W    | 0×00000000     | Packet handler<br>configuration                        |

| MIPIC_GEN_VCID              | 0x00030 | W    | 0x00000000     | ~                                                      |

| MIPIC_MODE_CFG              | 0x00034 | W    | 0x0000000      |                                                        |

| MIPIC_VID_MODE_C<br>FG      | 0x00038 | W    | 0x00000000     | Video mode configuration.                              |

| MIPIC_VID_PKT_SIZ<br>E      | 0x0003c | W    | 0x00000000     |                                                        |

| MIPIC_VID_NUM_CH<br>UNKS    | 0x00040 | W    | 0×00000000     | $\langle \mathcal{O} \rangle$                          |

| MIPIC_VID_NULL_SI<br>ZE     | 0x00044 | W    | 0×00000000     |                                                        |

| MIPIC_VID_HSA_TIM<br>E      | 0x00048 | W    | 0×00000000     | Line timing configuration.                             |

| MIPIC_VID_HBP_TIM<br>E      | 0x0004c | w    | 0x00000000     | $\bigcirc$                                             |

| MIPIC_VID_HLINE_T<br>IME    | 0x00050 | w    | 0x0000000      | )                                                      |

| MIPIC_VID_VSA_LIN<br>ES     | 0x00054 | w    | 0x00000000     | Vertical timing configuration.                         |

| MIPIC_VID_VBP_LIN<br>ES     | 0x00058 | w    | 0×00000000     |                                                        |

| MIPIC_VID_VFP_LIN<br>ES     | 0x0005c | w    | 0x00000000     |                                                        |

| MIPIC_VID_VACTIVE<br>_LINES | 0x00060 | w    | 0x00000000     |                                                        |

| MIPIC_EDPI_CMD_SI<br>ZE     | 0x00064 | W    | 0x00000000     |                                                        |

| MIPIC_CMD_MODE_<br>CFG      | 0x00068 | w    | 0x00000000     | Command mode configuration                             |

| MIPIC_GEN_HDR               | 0x0006c | W    | 0x00000000     | Generic packet header configuration.                   |

| MIPIC_GEN_PLD_DA<br>TA      | 0x00070 | w    | 0x00000000     | Generic payload data in and out.                       |

| MIPIC_CMD_PKT_ST<br>ATUS    | 0x00074 | w    | 0x00000000     | Command packet status                                  |

| MIPIC_TO_CNT_CFG            | 0x00078 | w    | 0x00000000     | Timeout timers configuration                           |

| Name                        | Offset  | Size | Reset<br>Value | Description                                                        |

|-----------------------------|---------|------|----------------|--------------------------------------------------------------------|

| MIPIC_HS_RD_TO_C<br>NT      | 0x0007c | w    | 0x00000000     |                                                                    |

| MIPIC_LP_RD_TO_C<br>NT      | 0x00080 | w    | 0x00000000     |                                                                    |

| MIPIC_HS_WR_TO_C<br>NT      | 0x00084 | w    | 0x00000000     |                                                                    |

| MIPIC_LP_WR_TO_C<br>NT      | 0x00088 | w    | 0x00000000     |                                                                    |

| MIPIC_BTA_TO_CNT            | 0x0008c | W    | 0x0000000      | •                                                                  |

| MIPIC_LPCLK_CTRL            | 0x00094 | W    | 0x0000000      |                                                                    |

| MIPIC_PHY_TMR_LP<br>CLK_CFG | 0x00098 | w    | 0x00000000     |                                                                    |

| MIPIC_PHY_TMR_CF<br>G       | 0x0009c | w    | 0x00000000     | D-PHY timing<br>configuration                                      |

| MIPIC_PHY_RSTZ              | 0x000a0 | W    | 0x0000000      | D-PHY reset control                                                |

| MIPIC_PHY_IF_CFG            | 0x000a4 | W    | 0x00000000     | D-PHY interface<br>configuration                                   |

| MIPIC_PHY_ULPS_CT<br>RL     | 0x000a8 | w    | 0x0000000      | D-PHY PPI interface<br>control                                     |

| MIPIC_PHY_TX_TRIG<br>GERS   | 0x000ac | w    | 0x0000000      | $\sim$                                                             |

| MIPIC_PHY_STATUS            | 0x000b0 | w    | 0×00000000     | D-PHY PPI status<br>interface                                      |

| MIPIC_PHY_TST_CT<br>RL0     | 0x000b4 | w    | 0x0000001      |                                                                    |

| MIPIC_PHY_TST_CT<br>RL_1    | 0x000b8 | w    | 0×00000000     |                                                                    |

| MIPIC_ERROR_ST0             | 0x000bc | W    | 0×00000000     | Interrupt status register<br>0                                     |

| MIPIC_ERROR_ST1             | 0x000c0 | w    | 0x00000000     | Interrupt status register<br>1                                     |

| MIPIC_MSK0                  | 0x000c4 | w    | 0×00000000     | Masks the interrupt<br>generation triggerd by<br>the ERROR_ST0 reg |

| MIPIC_MSK1                  | 0x000c8 | w    | 0×00000000     | Masks the interrupt<br>generation triggerd by<br>the ERROR_ST1 reg |

| MIPIC_INT_FORCE0            | 0x000d8 | W    | 0x0000000      |                                                                    |

| MIPIC_INT_FORCE1            | 0x000dc | W    | 0x0000000      |                                                                    |

| MIPIC_VID_SHADO<br>W_CTRL   | 0x00100 | w    | 0x00000000     |                                                                    |

| MIPIC_Copy0<br>DPI_VCID     | 0x0010c | w    | 0x00000000     | The DPI interface configuration.                                   |

| Name                                | Offset  | Size | Reset<br>Value | Description                                            |

|-------------------------------------|---------|------|----------------|--------------------------------------------------------|

| MIPIC_Copy0<br>DPI_COLOR_CODIN<br>G | 0x00110 | w    | 0×00000000     |                                                        |

| MIPIC_Copy0<br>LP_CMD_TIM           | 0x00118 | w    | 0×00000000     | Low-power Command<br>Timing Configuration<br>Register. |

| MIPIC_Copy0<br>VID_MODE_CFG         | 0x00138 | w    | 0×00000000     | Video mode configuration.                              |

| MIPIC_Copy0<br>VID_PKT_SIZE         | 0x0013c | w    | 0x00000000     |                                                        |

| MIPIC_Copy0<br>VID_NUM_CHUNKS       | 0x00140 | w    | 0×00000000     |                                                        |

| MIPIC_Copy0<br>VID_NULL_SIZE        | 0x00144 | w    | 0x00000000     |                                                        |

| MIPIC_Copy0<br>VID_HSA_TIME         | 0x00148 | W    | 0x0000000      | Line timing configuration.                             |

| MIPIC_Copy0<br>VID_HBP_TIME         | 0x0014c | w    | 0x0000000      |                                                        |

| MIPIC_Copy0<br>VID_HLINE_TIME       | 0x00150 | w    | 0x0000000      |                                                        |

| MIPIC_Copy0<br>VID_VSA_LINES        | 0x00154 | w    | 0×00000000     | Vertical timing configuration.                         |

| MIPIC_Copy0<br>VID_VBP_LINES        | 0x00158 | w    | 0×00000000     | )                                                      |

| MIPIC_Copy0<br>VID_VFP_LINES        | 0x0015c | w    | 0×00000000     |                                                        |

| MIPIC_Copy0<br>VID_VACTIVE_LINES    | 0x00160 | w    | 0x00000000     |                                                        |

Notes:<u>Size</u>:**B**- Byte (8 bits) access, **HW**- Half WORD (16 bits) access, **W**-WORD (32 bits) access

# **37.4.2 Detail Register Description**

## MIPIC\_VERSION

Address: Operational Base + offset (0x00000) Version of the mipi controller

| Bit  | Attr | Reset Value | Description                                  |

|------|------|-------------|----------------------------------------------|

| 31:0 | RO   | 0x3133302a  | version                                      |

| 51.0 | ĸo   | 0731333029  | indicates the version of the mipi_controller |

#### MIPIC\_PWR\_UP

Address: Operational Base + offset (0x00004)

Core power-up

| Bit  | Attr | <b>Reset Value</b> | Description |

|------|------|--------------------|-------------|

| 31:1 | RO   | 0x0                | reserved    |

| Bit | Attr | Reset Value | Description                                 |

|-----|------|-------------|---------------------------------------------|

|     |      |             | shutdownz                                   |

|     |      |             | This bit indicates the core power-up or the |

| 0   | RW   | 0x0         | reset                                       |

|     |      |             | 0-Reset                                     |

|     |      |             | 1-Power-up                                  |

## MIPIC\_CLKMGR\_CFG

Address: Operational Base + offset (0x00008) Configuration of the internal clock dividers

| Bit    | Attr | Reset Value                             | Description                                      |

|--------|------|-----------------------------------------|--------------------------------------------------|

| 31:16  | RO   | 0x0                                     | reserved                                         |

|        |      |                                         | TO_CLK_DIVISION                                  |

|        |      |                                         | This field indicates the division factor for the |

| 15:8   | RW   | 0x00                                    | Time Out clock used as the timing unit in the    |

|        |      |                                         | configuration of HS to LP and LP to HS           |

|        |      |                                         | transition error.                                |

|        |      |                                         | TX_ESC_CLK_DIVISION                              |

|        |      |                                         | Field0000 Abstract                               |

| 7:0    | RW   | 0.400                                   | This field indicates the division factor for the |

| 7:0 KW | 0x00 | TX_Escape clock source(lanebyteclk).The |                                                  |

|        |      |                                         | value 0 and 1 stop the TX_ESC clock              |

|        |      | generation                              |                                                  |

## MIPIC\_DPI\_VCID

Address: Operational Base + offset (0x0000c) The DPI interface configuration.

| Bit  | Attr | <b>Reset Value</b> | Description                                                                                               |

|------|------|--------------------|-----------------------------------------------------------------------------------------------------------|

| 31:2 | RO   | 0x0                | reserved                                                                                                  |

| 1:0  | RW   |                    | dpi_vid<br>This field configures the DPI virtual channel id<br>that is indexed to the Video mode packets. |

|      |      |                    |                                                                                                           |

# MIPIC\_DPI\_COLOR\_CODING

Address: Operational Base + offset (0x00010)

| Bit  | Attr | Reset Value | Description                                |

|------|------|-------------|--------------------------------------------|

| 31:9 | RO   | 0x0         | reserved                                   |

|      |      |             | en18_loosely                               |

| 8    | RW   | 0x0         | When set to 1, this bit enables 18 loosely |

|      |      |             | packed pixel stream.                       |

| 7:4  | RO   | 0x0         | reserved                                   |

| Bit | Attr | Reset Value | Description                                   |

|-----|------|-------------|-----------------------------------------------|

|     |      |             | dpi_color_coding                              |

|     |      |             | This field configures the DPI color coding as |

|     |      |             | follows:                                      |

|     |      |             | 000:16bit configuration 1                     |

| 3:0 | RW   | 0x0         | 001:16bit configuration 2                     |

|     |      |             | 010:16bit configuration 3                     |

|     |      |             | 011:18bit configuration 1                     |

|     |      |             | 100:18bit configuration 2                     |

|     |      |             | 101:24bit                                     |

# MIPIC\_DPI\_CFG\_POL

Address: Operational Base + offset (0x00014)

| Bit  | Attr | Reset Value | Description                                     |

|------|------|-------------|-------------------------------------------------|

| 31:5 | RO   | 0x0         | reserved                                        |

|      |      |             | colorm_active_low                               |

| 4    | RW   | 0x0         | When set to 1, this bit configures the color    |

|      |      |             | mode pin as active low                          |

|      |      |             | shutd_active_low                                |

| 3    | RW   | 0x0         | When set to 1, this bit configures the shut     |

|      |      |             | down pin as active low                          |

|      |      |             | hsync_active_low                                |

| 2    | RW   | 0x0         | When set to 1, this bit configures the          |

|      |      |             | horizontal synchronism pin as active low.       |

|      |      |             | vsync_active_low                                |

| 1    | RW   | 0x0         | When set to 1, this bit configures the vertical |

|      |      |             | synchronism pin as active low                   |

|      |      |             | dataen_active_low                               |

| 0    | RW   | 0x0         | When set to 1, this bit configures the data     |

|      |      |             | enable pin as active low                        |

## MIPIC\_LP\_CMD\_TIM

Address: Operational Base + offset (0x00018) Low-power Command Timing Configuration Register.

| P | Bit   | Attr | Reset Value | Description |

|---|-------|------|-------------|-------------|

|   | 31:24 | RO   | 0x0         | reserved    |

| Bit   | Attr | Reset Value | Description                                                       |

|-------|------|-------------|-------------------------------------------------------------------|

|       |      |             | outvact_lpcmd_time<br>outside VACT region command time.This field |

|       |      |             | configures the time available to transmit a                       |

|       |      |             | command in low-power mode.The time value                          |

|       |      |             | is expressed in a number of bytes format. The                     |

| 23:16 | RW   | 0x00        | number of bytes represents the maximum                            |

|       |      |             | size of a packet that can fit in a line during the                |

|       |      |             | VSA,VBP,and VFP region.                                           |

|       |      |             | This field must be configured with a value                        |

|       |      |             | greater than or equal to four bytes to allow the                  |

|       |      |             | transmission of the DCTRL commands such as                        |

|       |      |             | shutdown and colorm in low-power mode.                            |

| 15:8  | RO   | 0x0         | reserved                                                          |

|       |      | 0×00        | invact_lpcmd_time                                                 |

|       |      |             | Inside VACT region command time. This field                       |

|       |      |             | configures the time available to transmit a                       |

| 7:0   |      |             | command in low-power mode.The time value                          |

| 7:0   | RW   |             | is expressed in a number of bytes format. The                     |

|       |      |             | number of bytes represents the maximum                            |

|       |      |             | size of the packet that can fit a line during the                 |

|       |      |             | VACT region.                                                      |

MIPIC\_PCKHDL\_CFG Address: Operational Base + offset (0x0002c) Packet handler configuration

| Bit  | Attr | Reset Value | Description                                |

|------|------|-------------|--------------------------------------------|

| 31:5 | RO   | 0x0         | reserved                                   |

|      |      |             | en_CRC_rx                                  |

| 4    | RW   | 0x0         | When set to 1, this bit enables the CRC    |

|      |      |             | reception and error reporting              |

|      | C    | YC          | en_ECC_rx                                  |

| 3    | RW   | 0x0         | When set to 1, this bit enables the ECC    |

|      |      |             | reception, error correction, and reporting |

|      |      |             | en_BTA                                     |

| 2    | RW   | 0x0         | When set to 1, this bit enables the Bus    |

|      |      |             | Turn-Around(BTA) request.                  |

|      | RW   | 0x0         | en_EOTp_rx                                 |

| 1    |      |             | Field0000 Abstract                         |

| 1    |      |             | When set to 1, this bit enables the EOTp   |

|      |      |             | reception                                  |

|      |      | 0×0         | en_EOTp_tx                                 |

| 0    | RW   |             | Field0000 Abstract                         |

|      |      |             | When set to 1,this bit enables the EOTp    |

|      |      |             | transmission                               |

#### MIPIC\_GEN\_VCID

Address: Operational Base + offset (0x00030)

| Bit  | Attr | Reset Value | Description                             |

|------|------|-------------|-----------------------------------------|

| 31:2 | RO   | 0x0         | reserved                                |

|      |      |             | gen_vcid_rx                             |

| 1:0  | RW   | 0x0         | the Generic interface read-back virtual |

|      |      |             | channel identification                  |

#### MIPIC\_MODE\_CFG

Address: Operational Base + offset (0x00034)

| Bit  | Attr | Reset Value | Description                                   |

|------|------|-------------|-----------------------------------------------|

| 31:1 | RO   | 0x0         | reserved                                      |

|      |      |             | en_video_mode                                 |

| 0    | RW   | 0x0         | When set to 1, this bit enables the DPI Video |

|      |      |             | mode transmission.                            |

# MIPIC\_VID\_MODE\_CFG

Address: Operational Base + offset (0x00038) Video mode configuration.

| Bit   | Attr | Reset Value | Description                                                                                                              |

|-------|------|-------------|--------------------------------------------------------------------------------------------------------------------------|

| 31:25 | RO   | 0x0         | reserved                                                                                                                 |

| 24    | RW   | 0×0         | vpg_orientation<br>This field indicates the color bar orientation as<br>follows:<br>0:Vertical mode<br>1:Horizontal mode |

| 23:21 | RO   | 0x0         | reserved                                                                                                                 |

| 20    | RW   | 0×0         | vpg_mode<br>This field is to select the pattern<br>0:Color bar(horizontal or vertical)<br>1:BER pattern(vertical only)   |

| 19:17 | RO   | 0x0         | reserved                                                                                                                 |

| 16    | RW   | 0×0         | vpg_en<br>When set to 1,this bit enables the video mode<br>pattern generator                                             |

| 15    | RW   | 0×0         | lpcmden<br>When set to 1,this bit enables the command<br>transmission only in low-power mode                             |

| 14    | RW   | 0×0         | frame_BTA_ack<br>When set to 1,this bit enables the request for<br>an acknowledge response at the end of a<br>frame      |

| Bit | Attr | Reset Value | Description                                                                                                                                                                                 |

|-----|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13  | RW   | 0x0         | en_lp_hfp<br>When set to 1,this bit enables the return to<br>low-power inside the HFP period when timing<br>allows.                                                                         |

| 12  | RW   | 0x0         | en_lp_hbp<br>When set to 1,this bit enables the return to<br>low-power inside the HBP period when timing<br>allows.                                                                         |

| 11  | RW   | 0x0         | en_lp_vact<br>When set to 1,this bit enables the return to<br>low-power inside the VACT period when<br>timing allows.                                                                       |

| 10  | RW   | 0×0         | en_lp_vfp<br>When set to 1,this bit enables the return to<br>low-power inside the VFP period when timing<br>allows.                                                                         |

| 9   | RW   | 0×0         | en_lp_vbp<br>When set to 1,this bit enables the return to<br>low-power inside the VBP period when timing<br>allows.                                                                         |

| 8   | RW   | 0x0         | en_lp_vsa<br>When set to 1,this bit enables the return to<br>low-power inside the VSA period when timing<br>allows.                                                                         |

| 7:2 | RO   | 0x0         | reserved                                                                                                                                                                                    |

| 1:0 | RW   | 0×0         | vid_mode_type<br>This field indicates the video mode<br>transmission type as follows:<br>00:Non-burst with sync pulses<br>01:Non-burst with sync events<br>10 and 11:Burst with sync pulses |

# MIPIC\_VID\_PKT\_SIZE

Address: Operational Base + offset (0x0003c)

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                         |

|-------|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:14 | RO   | 0x0         | reserved                                                                                                                                                                                            |

| 13:0  | RW   | 0×0000      | vid_pkt_size<br>This field configures the number of pixels on a<br>single vedio packet.if you use the 18-bit mode<br>and do not enable loosely packed stream,this<br>vaule must be a multiple of 4. |

# MIPIC\_VID\_NUM\_CHUNKS

Address: Operational Base + offset (0x00040)

| Bit     | Attr | Reset Value | Description                                                 |

|---------|------|-------------|-------------------------------------------------------------|

| 31:13   | RO   | 0x0         | reserved                                                    |

|         |      | 0×0000      | num_chunks<br>This field configures the number of chunks to |

| 12:0 RW | RW   |             | be transmitted during a line period(a chunk is              |

|         |      |             | a video packet or a null packet)                            |

# MIPIC\_VID\_NULL\_SIZE

Address: Operational Base + offset (0x00044)

| Bit   | Attr | Reset Value | Description                                                                    |

|-------|------|-------------|--------------------------------------------------------------------------------|

| 31:13 | RO   | 0x0         | reserved                                                                       |

| 12:0  | RW   | 0×0000      | null_pkt_size<br>This field configures the number of bytes in a<br>null packet |

#### MIPIC\_VID\_HSA\_TIME

Address: Operational Base + offset (0x00048) Line timing configuration.

| Bit   | Attr | <b>Reset Value</b> | Description                                                                                                 |

|-------|------|--------------------|-------------------------------------------------------------------------------------------------------------|

| 31:12 | RO   | 0x0                | reserved                                                                                                    |

| 11:0  | RW   | 0×000              | hsa_time<br>This field configures the Horizontal<br>Synchronism Active period in lane byte clock<br>cycles. |

# MIPIC\_VID\_HBP\_TIME

Address: Operational Base + offset (0x0004c)

| Bit   | Attr | Reset Value | Description                                                                                     |

|-------|------|-------------|-------------------------------------------------------------------------------------------------|

| 31:12 | RO   | 0x0         | reserved                                                                                        |

| 11:0  | RW   |             | hbp_time<br>This field configures the Horizontal Back Porch<br>period in lane byte clock cycles |

|       |      |             |                                                                                                 |

## MIPIC\_VID\_HLINE\_TIME

Address: Operational Base + offset (0x00050)

| Bit   | Attr | Reset Value | Description                                       |

|-------|------|-------------|---------------------------------------------------|

| 31:15 | RO   | 0x0         | reserved                                          |

|       |      |             | hline_time                                        |

| 14:0  | RW   | 0x0000      | This field configures the size of the total lines |

|       |      |             | counted in lane byte cycles.                      |

# MIPIC\_VID\_VSA\_LINES

Address: Operational Base + offset (0x00054) Vertical timing configuration.

| Bit   | Attr | <b>Reset Value</b> | Description                                    |

|-------|------|--------------------|------------------------------------------------|

| 31:10 | RO   | 0x0                | reserved                                       |

|       |      | 0x000              | vsa_lines                                      |

| 9:0   | RW   |                    | This field configures the Vertical Synchronism |

| 9.0   |      |                    | Active period measured in number of            |

|       |      |                    | horizontal lines.                              |

#### MIPIC\_VID\_VBP\_LINES

Address: Operational Base + offset (0x00058)

| Bit   | Attr | Reset Value | Description                                   |

|-------|------|-------------|-----------------------------------------------|

| 31:10 | RO   | 0x0         | reserved                                      |

|       |      |             | vbp_lines                                     |

| 9:0   | RW   | 0x000       | This field configures the Vertical Back Porch |

|       |      |             | period measured in horizontal lines.          |

#### MIPIC\_VID\_VFP\_LINES

Address: Operational Base + offset (0x0005c)

| Bit   | Attr | <b>Reset Value</b> | Description                                                                                         |

|-------|------|--------------------|-----------------------------------------------------------------------------------------------------|

| 31:10 | RO   | 0x0                | reserved                                                                                            |

| 9:0   | RW   |                    | vfp_lines<br>This field configures the Vertical Front Porch<br>period measured in horizontal lines. |

#### MIPIC\_VID\_VACTIVE\_LINES

Address: Operational Base + offset (0x00060)

| Bit   | Attr       | Reset Value | Description                                      |

|-------|------------|-------------|--------------------------------------------------|

| 31:14 | RO         | 0x0         | reserved                                         |

|       | $\bigcirc$ |             | v_active_line                                    |

| 13:0  | RW         | 0x0000      | This field configures the Vertical Active period |

|       |            |             | measured in horizontal lines.                    |

#### MIPIC\_EDPI\_CMD\_SIZE

Address: Operational Base + offset (0x00064)

| Bit   | Attr | Reset Value | Description |

|-------|------|-------------|-------------|

| 31:16 | RO   | 0x0         | reserved    |

| Bit  | Attr | Reset Value | Description                                |

|------|------|-------------|--------------------------------------------|

|      |      | 0×0000      | edpi_allowed_cmd_size                      |

| 15:0 |      |             | This field configures the maximum allowed  |

|      | RW   |             | size for an eDPI write memory              |

|      |      |             | command, measured in pixels. Automatic     |

|      |      |             | partitioning of data obtained from eDPI is |

|      |      |             | permanently enabled.                       |

# MIPIC\_CMD\_MODE\_CFG

Address: Operational Base + offset (0x00068) Command mode configuration

| 31:25       RO       0x0       reserved         24       RW       0x0       max_rd_pkt_size<br>This bit configures the maximum read packet<br>size command transmission type:<br>0:High-speed<br>1:Low-power         23:20       RO       0x0       reserved         23:20       RO       0x0       reserved         19       RW       0x0       dcs_lw_tx<br>This bit configures the DCS long write packet<br>command transmission type:<br>0:high-speed<br>1:low-power         18       RW       0x0       dcs_sr_0p_tx<br>This bit configures the DCS short read packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         17       RW       0x0       dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         17       RW       0x0       dcs_sw_0p_tx                                                                                                                                                                                                                                                                           | and mode configuration |      |             |                                                |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------------|------------------------------------------------|--|--|

| 24       RW       0x0       max_rd_pkt_size<br>This bit configures the maximum read packet<br>size command transmission type;<br>0:High-speed<br>1:Low-power         23:20       RO       0x0       reserved         19       RW       0x0       reserved         19       RW       0x0       dcs_lw_tx<br>This bit configures the DCS long write packet<br>command transmission type:<br>0:high-speed<br>1:low-power         18       RW       0x0       dcs_sr_0p_tx<br>This bit configures the DCS short read packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         17       RW       0x0       dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power | Bit                    | Attr | Reset Value | Description                                    |  |  |

| 24RW0x0This bit configures the maximum read packet<br>size command transmission type:<br>0:High-speed<br>1:Low-power23:20RO0x0reserved23:20RO0x0reserved19RW0x0dcs_lw_tx<br>This bit configures the DCS long write packet<br>command transmission type:<br>0:High-speed<br>1:low-power19RW0x0dcs_lw_tx<br>This bit configures the DCS long write packet<br>command transmission type:<br>0:High-speed<br>1:low-power18RW0x0dcs_sr_0p_tx<br>This bit configures the DCS short read packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power17RW0x0dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power16RW0x0dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power16RW0x0dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power                                                                                                                          | 31:25                  | RO   | 0x0         | reserved •                                     |  |  |

| 24       RW       0x0       size command transmission type:         23:20       RO       0x0       reserved         23:20       RO       0x0       reserved         19       RW       0x0       cdcs_lw_tx         19       RW       0x0       command transmission type:         0:high-speed       0:high-speed         1:low-power       0:high-speed         18       RW       0x0         18       RW       0x0         17       RW       0x0         16       RW       0x0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |      |             |                                                |  |  |

| 16       RW       0x0       reserved         11       RW       0x0       reserved         19       RW       0x0       command transmission type:         110w-power       0:high-speed       0:high-speed         110w-power       dcs_sr_0p_tx         18       RW       0x0       dcs_sr_0p_tx         18       RW       0x0       dcs_sw_1p_tx         17       RW       0x0       dcs_sw_1p_tx         16       RW       0x0       dcs_sw_0p_tx         16       RW       0x0       dcs_sw_0p_tx         16       RW       0x0       dcs_sw_0p_tx         16       RW       0x0       dcs_sw_0p_tx         11       rhis bit configures the DCS short write packet with zero parameter command transmission type:       0:High-speed         11       RW       0x0       dcs_sw_0p_tx         11       RW       0x0       dcs_sw_0p_tx         11       RW       0x0       dcs_sw_0p_tx <t< td=""><td></td><td></td><td></td><td></td></t<>                                    |                        |      |             |                                                |  |  |

| 1:Low-power         23:20       RO       0x0       reserved         19       RW       0x0       dcs_lw_tx<br>This bit configures the DCS long write packet<br>command transmission type:<br>0:high-speed<br>1:low-power         18       RW       0x0       dcs_sr_0p_tx<br>This bit configures the DCS short read packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         17       RW       0x0       dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power                                                                                                                                                                                               | 24                     | RW   | 0x0         | size command transmission type:                |  |  |

| 23:20       RO       0x0       reserved         19       RW       0x0       dcs_lw_tx<br>This bit configures the DCS long write packet<br>command transmission type:<br>0:high-speed<br>1:low-power         18       RW       0x0       dcs_sr_0p_tx<br>This bit configures the DCS short read packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         17       RW       0x0       dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power                                                                                                                                                                                                                   |                        |      |             | 0:High-speed                                   |  |  |

| 19       RW       0x0       dcs_lw_tx<br>This bit configures the DCS long write packet<br>command transmission type:<br>0:high-speed<br>1:low-power         18       RW       0x0       dcs_sr_0p_tx<br>This bit configures the DCS short read packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         17       RW       0x0       dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power                                                                                                                                                                                                                                                                   |                        |      |             | 1:Low-power                                    |  |  |

| 19RW0x0This bit configures the DCS long write packet<br>command transmission type:<br>0:high-speed<br>1:low-power18RW0x0dcs_sr_0p_tx<br>This bit configures the DCS short read packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power17RW0x0dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power17RW0x0dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power16RW0x0dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power                                                                                                                                                                                                                                                                                                                                                                                                                              | 23:20                  | RO   | 0x0         | reserved                                       |  |  |

| 19       RW       0x0       command transmission type:<br>0:high-speed<br>1:low-power         18       RW       0x0       dcs_sr_0p_tx<br>This bit configures the DCS short read packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         17       RW       0x0       dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power                                                                                                                                                                                                                                                                                                                                 |                        |      |             | dcs_lw_tx                                      |  |  |

| 18       RW       0x0       0:high-speed<br>1:low-power         18       RW       0x0       dcs_sr_0p_tx<br>This bit configures the DCS short read packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         17       RW       0x0       dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power                                                                                                                                                                                                                                                                                                                                                               |                        |      |             | This bit configures the DCS long write packet  |  |  |

| 1:low-power         18       RW       0x0       dcs_sr_0p_tx<br>This bit configures the DCS short read packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         17       RW       0x0       dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power                                                                                                                                                                                                                                                                                                                                                                                                           | 19                     | RW   | 0x0         | command transmission type:                     |  |  |

| 18RW0x0dcs_sr_0p_tx<br>This bit configures the DCS short read packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power17RW0x0dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power16RW0x0dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power16RW0x0dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        |      |             | 0:high-speed                                   |  |  |

| 18RW0x0This bit configures the DCS short read packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power17RW0x0dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power16RW0x0dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power16RW0x0dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        |      |             | 1:low-power                                    |  |  |

| 18       RW       0x0       with zero parameter command transmission type:         0:High-speed       0:High-speed         17       RW       0x0       dcs_sw_1p_tx         17       RW       0x0       dcs_sw_1p_tx         16       RW       0x0       dcs_sw_0p_tx         17       RW       0x0       dcs_sw_0p_tx         18       Discover       0:High-speed         19       Disped       0:High-speed         11       Disped       0:High-speed         11       Disped       0:High-speed         12       Disped       0:High-speed         13       Disped       1:Low-power                                                                                                                                                                               |                        |      |             | dcs_sr_0p_tx                                   |  |  |

| 18       RW       0x0       type:<br>0:High-speed<br>1:Low-power         17       RW       0x0       dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |      | 0.40        | This bit configures the DCS short read packet  |  |  |

| 17       RW       0x0       dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18                     |      |             | with zero parameter command transmission       |  |  |

| 16       RW       0x0       1:Low-power         17       RW       0x0       dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power         16       RW       0x0       dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10                     |      | 0.0         | type:                                          |  |  |

| 17RW0x0dcs_sw_1p_tx<br>This bit configures the DCS short write packet<br>with one parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power16RW0x0dcs_sw_0p_tx<br>This bit configures the DCS short write packet<br>with zero parameter command transmission<br>type:<br>0:High-speed<br>1:Low-power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        |      | C Y         | 0:High-speed                                   |  |  |